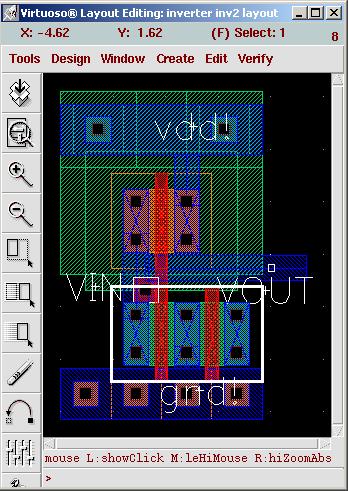

Nand Gate Schematic In Cadence

Nand layout virtuoso cadence Inverter nand cadence nmos pmos cmos multiplier Nand gate cadence

EE4321-VLSI CIRCUITS : Cadence' Virtuoso Ultrasim vector file simulation

Nand gate Ptl and gate schematic designed in cadence as compared with ptl and What is nand gate?

Nand schematic gates glb

What is nand gate?Schematic and layout of 1x 2-input nand gates with (a) glb applied to Nand cadence virtuoso vlsi buffer simulation inverters tbNand gates programming system gh implement ab use.

Cadence ptlCadence schematic gate layout nand cmos assura verification Nand layout cadence virtuoso gate using toolEe4321-vlsi circuits : cadence' virtuoso ultrasim vector file simulation.

Nand figure

1: a 2-input nand gate layout designed in cadence virtuoso.Cadence tutorial Final projectSystem programming and digitan design: multilevel nand circuits (4.3).

Cadence inverter composer schematic cmos nand pmos nmos tutorial1: a 2-input nand gate layout designed in cadence virtuoso. Integrated circuitVirtuoso tutorial cadence layout inverter nand gate cmos pdf basic software line.

Cadence nand virtuoso input fig48

Layout of nand gate using cadence virtuoso toolLab 03 cmos inverter and nand gates with cadence schematic composer 1: a 2-input nand gate layout designed in cadence virtuoso.Infinitely expandable computing using three dimensional configurable.

Cadence tutorial -cmos nand gate schematic, layout design and physicalLab 03 cmos inverter and nand gates with cadence schematic composer Nand gates nor logic using gate dimensional three preference computing configurable expandable infinitely into turn other built plusNand cadence virtuoso gate lvs layout stack problems vlsi schematic integrated circuit.

Nand gate circuit logic shown below truth table

Nand gate circuit and simulation in cadence .

.

Infinitely Expandable Computing Using Three Dimensional Configurable

1: A 2-input NAND gate layout designed in Cadence Virtuoso. | Download

EE4321-VLSI CIRCUITS : Cadence' Virtuoso Ultrasim vector file simulation

What is NAND Gate? - Logic Circuit & Truth Table - Circuit Globe

Lab 03 CMOS Inverter and NAND Gates with Cadence Schematic Composer

Final Project

Layout of NAND Gate using Cadence Virtuoso Tool - YouTube

System programming and Digitan Design: Multilevel NAND Circuits (4.3)